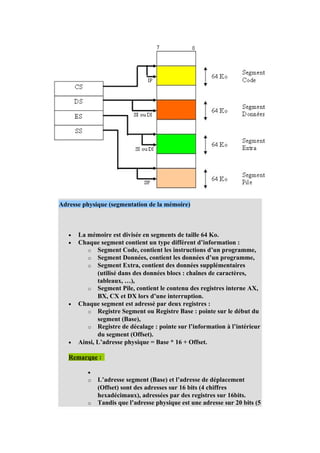

Ce document explique l'architecture du processeur 8088 en détaillant les différents types de registres, y compris le pointeur de base de la pile (bp), les registres d'index de source et de destination (si, di), et le pointeur d'instruction (ip). Il aborde également le registre d'état (flag) qui reflète les résultats d'opérations, ainsi que la gestion et la segmentation de la mémoire, mettant en évidence comment les segments sont adressés par des registres de base et de décalage. En outre, il décrit l'organisation de la mémoire divisée en segments pour le code, les données, les données supplémentaires et la pile.