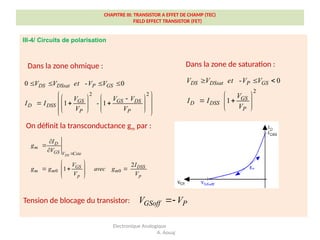

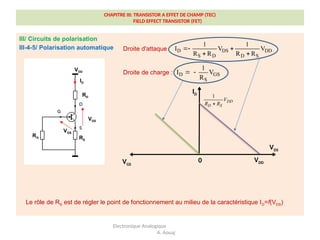

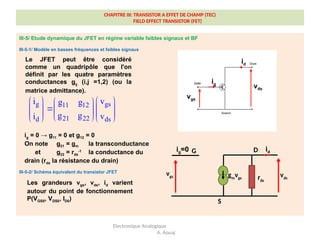

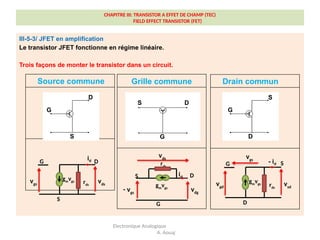

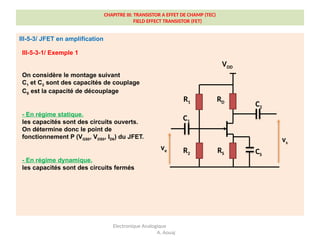

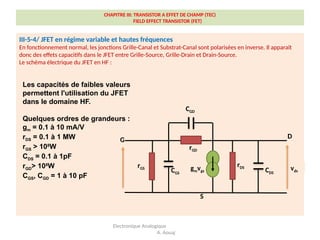

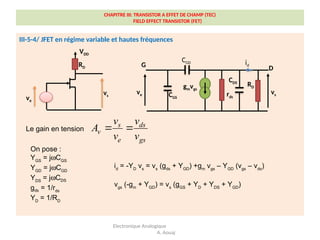

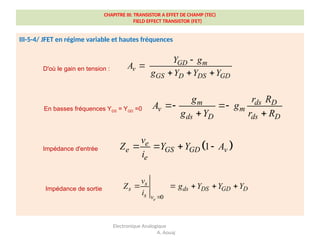

Le transistor à effet de champ (TEC ou FET) est un transistor unipolaire modulé par un champ électrique, générant du courant avec une commande en tension. Il existe des types tels que le JFET et le MOSFET, ayant des caractéristiques comme une impédance d'entrée élevée et un faible bruit. Le document aborde également les circuits de polarisation et l'étude dynamique du JFET en régimes basse et haute fréquence.

![CHAPITRE III: TRANSISTOR A EFFET DE CHAMP (TEC)

FIELD EFFECT TRANSISTOR (FET)

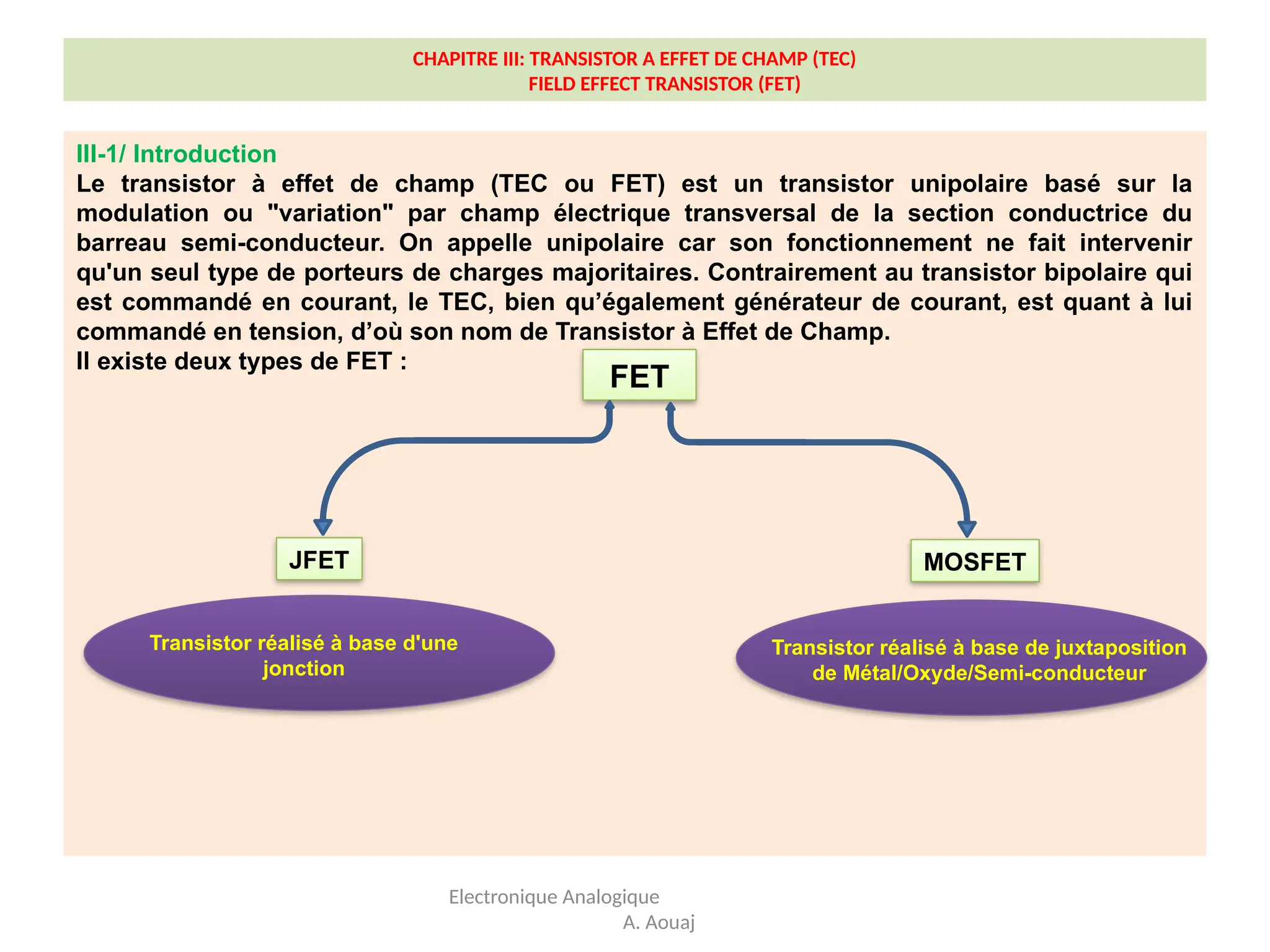

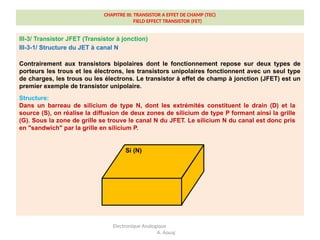

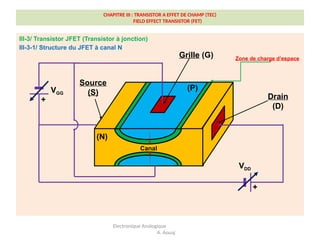

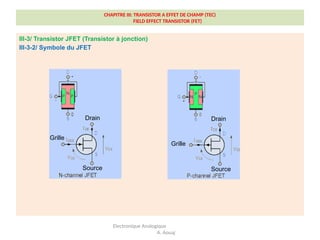

III-3/ Transistor JFET (Transistor à jonction)

III-3-3/ Principe de fonctionnement

On considère un transistor JFET à Canal N

Electronique Analogique

A. Aouaj

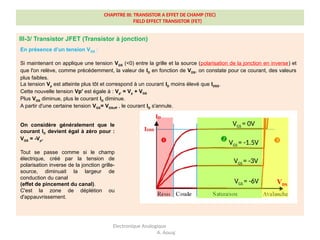

En l’absence de tension VGS :

Le canal drain-source conduit proportionnellement

avec l’augmentation de la tension VDS.

(Le transistor se comporte comme une résistance)

[Zone Ohmique (1)]

Pour une certaine valeur de VDS, le courant de drain

ID cesse de croître et devient constant.

C'est la tension de pincement ou Vp (tension de

(pinch-off) qui correspond au courant de saturation

ID que l’on appelle IDSS.

[Zone de saturation (2) ]

Zone coude

Courbe à VGS = 0V](https://image.slidesharecdn.com/courselecanalogch3transistorjfet-241218205118-501a4bb6/85/Cours-ELEC-ANALOG-CH3-TRANSISTOR_JFET-pptx-6-320.jpg)